This reference design is especially helpful in high-speed networking functions, knowledge facilities, and enterprise environments, the place dependable and scalable connectivity is important.

Gigabit Ethernet hyperlink aggregation is a vital know-how in fashionable networking, enabling larger bandwidth, improved redundancy, and enhanced community effectivity by combining a number of Ethernet hyperlinks right into a single logical connection. For design engineers, a Gigabit Ethernet hyperlink aggregator reference design serves as a worthwhile useful resource to streamline improvement, optimize efficiency, and guarantee seamless knowledge transmission. It supplies a examined framework with {hardware} and software program pointers, lowering design complexities and accelerating time to market.

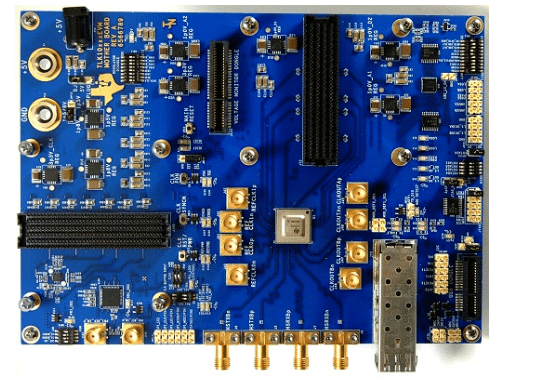

The Gigabit Ethernet Hyperlink Aggregator reference design TIDA-00269 by Texas Devices (TI) options the TLK10081, a multi-rate hyperlink aggregator engineered for high-speed bi-directional point-to-point knowledge transmission. By multiplexing lower-speed serial hyperlinks right into a single higher-speed hyperlink, this design considerably reduces the variety of bodily connections required, simplifying system implementation and administration. The TLK10081 helps aggregation and de-aggregation of assorted serial hyperlinks, together with uncooked knowledge codecs, making it extremely versatile for various functions.

To enhance the TLK10081, this reference design incorporates the CDCM6208 system, which generates a particularly low-jitter clock enter. That is notably helpful for techniques that both lack an exterior clock supply or fail to satisfy jitter necessities. The design ensures seamless analysis of high-speed alerts by routing channel A alerts to SFP+ modules, that are generally utilized in optical fiber techniques. In the meantime, channel B alerts are routed to edge launch SMA connectors, facilitating simple testing utilizing customary check tools.

The TLK10081 helps numerous knowledge varieties with out specialised encoding, dealing with 1 GbE, SGMII, and uncooked knowledge at 250 Mbps to 1.25 Gbps. It allows 8 × (0.25–1.25 Gbps) to 1 × (2–10 Gbps) multiplexing for environment friendly hyperlink aggregation. With versatile clocking, together with externally jitter-cleaned clocks, it ensures sign integrity. Consuming simply 800mW per channel, it’s extremely energy-efficient. Its aggregation of a number of serial alerts right into a single high-speed hyperlink reduces cable complexity, whereas de-aggregation ensures seamless knowledge transmission.

This reference design is right for functions in each communications and industrial sectors. In communications, it may be utilized in optical community terminal models (ONTs) and WLAN/Wi-Fi entry factors. In industrial settings, it’s appropriate for air circuit breakers (ACBs), plane cockpit shows, digitizers (≥ 50MSPS), interconnect/distribution containers, energy analyzers, and programmable DC energy provides.

By using the Gigabit Ethernet Hyperlink Aggregator reference design, clients can streamline their knowledge transmission infrastructure, improve system efficiency, and cut back {hardware} complexity. The mixture of high-speed aggregation, versatile clocking, and low energy consumption makes this answer a sturdy alternative for high-speed networking and industrial functions.

TI has examined this reference design. It comes with a invoice of supplies (BOM), schematics, meeting drawing, printed circuit board (PCB) format, and extra. The corporate’s web site has further knowledge concerning the reference design. To learn extra about this reference design, click on right here.